# Evaluation of Aerosol Jet Printing (AJP) technology for electronic packaging and interconnect technique

S. Stoukatch<sup>a</sup>, P. Laurent<sup>a</sup>, S. Dricot<sup>a</sup>, F. Axisa<sup>a</sup>, L.Seronveaux<sup>b</sup>, D.Vandormael<sup>b</sup>, E.Beeckman<sup>b</sup>, B. Heusdens<sup>c</sup>, J. Destiné<sup>a</sup>

<sup>a</sup>EMMI/Microsys, University of Liège, 4000 Liège, Belgium

Tel: +32(0)4 246 62 55, E-mail: serguei.stoukatch@ulg.ac.be

<sup>b</sup>SIRRIS, Collective Centre of the Belgium Technology Industry, 4102, Liege Science park, Belgium

<sup>c</sup>TAIPRO Engineering, Rue du Bois Saint Jean, 15/17, 4102 Seraing, Belgium

#### **Abstract**

We evaluated suitability of AJP (Aerosol Jet Printing) deposited silver layer on variety of organic substrates for the most common interconnect techniques used for electronic packaging. Specifically, we checked if the AJP silver layer can be electrically interconnected by Au and Al wires bonding technique. We also evaluated suitability of AJP silver layer for surface-mount technology (SMT). We performed electrical characterization of the AJP silver layer. We realized a fully functional working prototype of Autonomous Wireless Sensor Node system using AJP silver conductive track as an electrical interconnection.

#### Introduction

Aerosol Jet Printing (AJP) is an innovative technology for a selective maskless deposition of wide range of materials (conductive, dielectric, biological, nanoparticles etc.) at micron-scale (minimum features of  $10\mu m$  line and  $10\mu m$  space are achieved). Because it is a contactless technology, it suits for application on any flat and non-flat, flexible and rigid substrates, and moreover for complex 3D systems. The technology is particularly unique for deposition of a conductive silver paste on plastic substrates. It is known that the organic substrates are particularly sensitive to thermal treatment, as a maximum temperature and time of thermal exposure. AJP silver layer has very low sintering temperature, as low as  $100\text{-}150^{\circ}\text{C}$ . The AJP silver layer fine pattern of  $10\mu m$  line and  $10\mu m$  space features is reportedly achieved [1-51]

That result is much better than a pattern realized by state-of-art a conventional screen printing technology there 100-150 $\mu$ m is an absolute minimum value of line/space features, and it is still better than a 30 $\mu$ m smallest features achieved by inkjet printing [6]. Remarkably, the conventional screen printing and inkjet printing technology are not suitable for 3D application.

Despite the advantages listed above the AJP technology remains still a novel technology there number issues must be studied and the technology is not yet widely accepted by industry.

## AJP deposition

We evaluated set of different samples there AJP silver pattern have been deposited using Optomec AJ300CE system. Sirris our research partner in the ongoing project is developing AJP silver deposition process. There are several commercially available silver inks that are suitable for AJP deposition; among them we selected the most common CSD-32 silver nano-dispersion, manufactured by Cabot. The ink

viscosity is 100 mPa.s. The CSD-32 silver ink comprises of engineered nanoparticles of 60 nm dimensions, and 45-50% weight in a liquid vehicle (glycol based solvent) [7].

During the deposition process the ink is supplied by the system into pneumatic activation mode by dry nitrogen (carrier and sheath gas). The ink has been deposited on the substrates and sequentially sintered by a laser. The laser of 100 mW power and 532nm wavelength generated 10 µm spot on freshly deposited silver layer. It requires only 100µs dwell tile to sinter the silver ink. Such short time of thermal exposure allows the thermal sintering on silver nano-ink, meanwhile the thermal sensitive plastic substrates remains at low temperature. The ink's manufacture recommends to perform sintering by mass curing process, there the ink and the substrate are subjected to temperature of 150°C for 30min. Sirris has been developed the sintering process there only the deposited ink is exposure to high temperature (estimated 100°C [8]) and the thermal sensitive plastic substrate remains at low temperature (below 80°C).

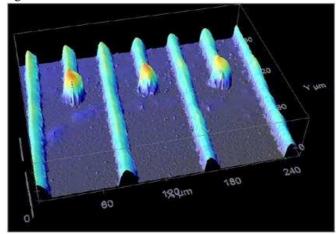

Once the silver pattern is sintered, it has been characterized using PLuNeox 3D optical profilometer. The example of topological characterization presented below on Fig.1.

Figure 1: Silver line of  $20\mu m$  width printed on a glass substrate.

## Wire bonding evaluation

For our investigation, the silver layer is deposited by AJP on following organic substrates: PI (polyimide, from DuPont trademark: Kapton) of  $25\mu m$  thickness, FR4 of 1.6mm thickness, 1 mm thick injected polycarbonate (PC) and 1 mm thick injected acrylonitrile butadiene styrene (ABS) . Some material such PI and FR4 are in widely used and become

conventional material as a board or as a carrier for the electronic assembly. Other material such PC and ABS are still less known for that. In the table 1 for your reference we listed the most important for the assembly mechanical and thermal properties of the organic substrates.

Table 1: Mechanical and thermal properties [10].

| Material | Tg,<br>°C | Operating temperature, °C | CTE,°<br>C/ppm | E-modulus,<br>GPa |

|----------|-----------|---------------------------|----------------|-------------------|

| FR4      | 150       | -55+125                   | 14/70          | 24                |

| PI       | 260       | -80+210                   | 20/n.a.        | 2.5               |

| PC       | 150       | -40+130                   | 65/n.a.        | 2.0-2.4           |

| ABS      | 105       | -20+80                    | 56/n.a.        | 2.3               |

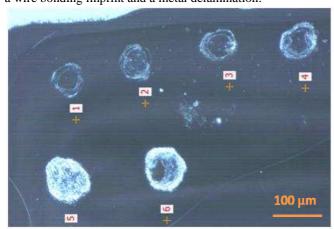

After fabrication the test samples, we assessed suitability of AJP deposited silver layer on 4 organic substrates in terms of different conventional interconnect techniques used for the electronic packaging[9] . Specifically, we checked if the AJP silver layer can be electrically interconnected by Au and Al wires bonding technique. We evaluated FR4, PI, PC and ABS substrates in terms of Au and Al wire bonding. Apparently the wire bonding on AJP deposited silver layer has limited bondability and a status as on the date of preparing the paper that the manufactured configuration can't be used for mass scale production. We tried to bond Au wire at 150°C, 120°C, 80°C and at room temperature to FR4 and PI substrate. For PC and ABS because its lower Tg, we used 80°C and at room temperature wire bonding. We also tried Al wire bonding (room temperature process) on FR4, PI, PC and ABS substrates. We observed several typical wire bonding failures: a wire bonding imprint and a metal delamination.

Figure 2: Au wire bonding imprint on surface of AJP silver layer deposited on ABS substrate.

Figure 3: Al wire bonding imprint on surface of AJP silver layer deposited on PC substrate.

There are number reasons that can cause a limited bondability for Au and Al wires. The silver AJP deposited layer has a relatively poor adhesion to the organic material underneath. The failure mode observed such bond pad peel suggests a poor adhesion of AJP layer to the carrier. The adhesion can be generally improved by adding the adhesion layer. We are also investigating the alternative cure conditions that we believed can improve that. Generally speaking, the wire bonding is more difficult on the plastic substrates; the plastic substrates are usually much softer or at least softer than the rigid substrates that are conventionally used for the wire bonding. An example of such material and substrates is as following: Si, SiO2, SiN, SiON and Al, Au, Ni. E-modules of the rigid substrate is above than 100 GPa, versus FR4 is 30 GPa and other tested materials as PI, PC, ABS have less than 3 GPa.

Based on the bonding trials we could not find a real problem of non-bondability, on one side the organic low E-modulus substrate causes the bondability issue and on another side we did not succeed to weld the wire bonds to the AJP deposited silver track even on harder substrate as FR4. The FR4 substrate normally suits for both, for Al and Au wedge wire bonding techniques.

The wire bonding on AJP deposited silver layer has limited bondability in terms of Au and Al wire bonding. We consider that fact as definitely not a drawback for the AJP technology; because of the idea to introduce the AJP silver conductive track as an alternative technique for the conventional interconnect technology, specifically for the wire bonding.

### **SMT** evaluation

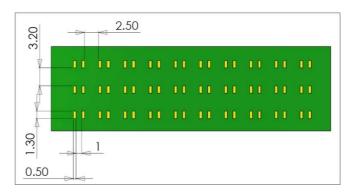

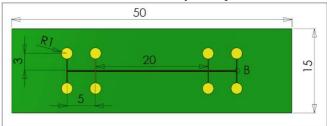

On all 4 plastic substrates: FR4, PI, PC and ABS we also evaluated suitability of AJP silver layer for surface-mount technology (SMT). The layout of the test substrate is depicted on figure 4. Each substrate comrises a matrix of 30 SMD footprints suitable for 0402 components placement.

Figure 4: Layout of the test substrate for SMT evaluation. All dimensions are in mm.

For that we tried two the most common SMT techniques, namely a reflow soldering and a conductive adhesive. As a pick and place tool for mounting components we used the automatic SMT pick and place system from Autotronik (Model: BS384V1). The system performs high accuracy mounting variety of SMT components as following: 01005, 0201, 0402, 0603, SOIC, PLCC, BGA,  $\mu$ BGA, CSP, QFP etc.

at placement rate up to 4000 UPH. Additionally to that, the system has a high precision dispensing system (suitable for solder and adhesives), bottom vision alignment system and can perform vision inspection before and after production. For the evaluation we used dummy SMD 0402 components.

We started the evaluation with a conductive isotropic adhesive. We investigated two curing schedule that differs by cure temperature and cure time: 3h at 80°C and 15min at 120°C. We placed SMD components on PC and ABS substrates and cured at 80°C and 120°C for PC and 80°C for ABS. Additionally for the adhesive method we evaluated soldering technique on higher Tg substrates as FR4 and PI. For the soldering we chosen conventional lead-free solder (melting point of 218°C and reflow temperature of 240°C). The soldering was not evaluated on lower Tg substrates as PC and ABS.

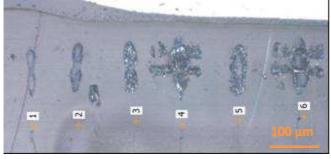

Figure 5: The SMD mounted on ABS with adhesive cured at 80°C.

Figure 6: The SMD mounted on PI with lead-free solder.

Figure 7: Typical observation of shear mode (SMD on FR4 attached by conductive glue and sheared).

The assembly has been inspected visually and evaluated by shear test and sequentially the failure mode for the shear test has been observed and characterized. The value for the shear test is in line with the results normally obtained on the rigid substrate with conventional finish and meets SMT specification. AJP deposited silver layer on all evaluated substrates (PI, FR4, PC and ABS) are suitable for surfacemount technology using conductive adhesive, and PI and FR4 are suitable for soldering technique.

#### **3D Printed Electronics**

Microsys laboratory realized a fully functional prototype of Autonomous Wireless Sensor Node. The system has unlimited autonomy because of energy harvesting features achieved by using a photovoltaic solar cells. The version with solar cells has a total volume of 1.2cm3 and extremely thin, the thickness is 2mm. The system is suitable for operation in standard ambient environment. As depicted on the figure 8, the system can be placed anywhere there is light present. The measurement rate is 2 units/min, working frequency is 868MHz and the system has extremely low power consumption of 100 microW. The working distance is 10 m indoor, and up to 100 m outdoor.

Figure 8: Fully functional prototype of Autonomous Wireless Sensor Node attached to the window frame.

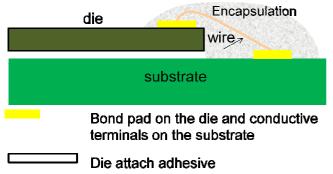

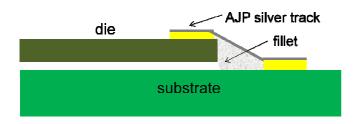

For the assembly of the first working prototype we used conventional interconnect technology adopted for flexible plastic substrates. Because of severe constrains on thermal budget for the total system, we may not use Au wire bonding technique to create the interconnection between the flexible substrate and the PV cell. The Au wire bonding requires at least 150°C stage temperature that is much too high for our system. For the concept proof, we assembled the system using Al wire bonding (a room temperature process), however Al wire bonding has several constrains that prevent the method from use it for a high scale production. The welded wires then are sequentially encapsulated by UV curable encapsulant that is also a room temperature process. To explore an alternative method to the wire bonding in order to provide the electrical interconnection between the flexible substrate to the die, we used AJP silver ink. The AJP silver track was deposited and laser sintered. In order to obtain a continuous conductive track between the terminal of the substrate and the bond pad on the die, we needed to prepare the sample in a specific way. As depicted on the figure 10, after the bonding the die to the substrate first we deposited a non-conductive fillet. The fillet has two main functions; first the fillet is to insulate the die side wall to prevent the die from the short circuit. The second function is to ensure the AJP silver track continuation. In principal the AJP track can be also deposited on the vertical wall, in our case on the die side wall, however it is more difficult to control the track thickness simultaneously both for

the horizontal and vertical surfaces during the deposition process.

Figure 9: Cross-sectional schematic view of the interconnect: a conventional sequence using wire bonding and encapsulation.

Figure 10: Cross-sectional schematic view on the interconnect: a realized by AJP silver layer.

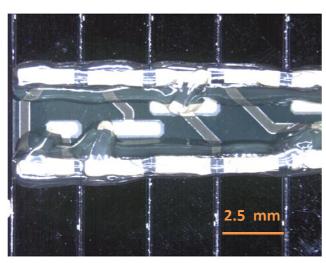

For the fillet material we used UV curable die adhesive. The prototype realized by AJP silver layer as a result of replacement wire bond by AJP silver layer, has a lower profile compare to the first prototype assembled using the conventional packaging technique. The newest prototype is inheritably thinner, it this case we reduced the total assembly thickness by 0.5 mm. Both prototypes have the same functionality. The figures 10 and 11depict the interconnect area for both prototypes.

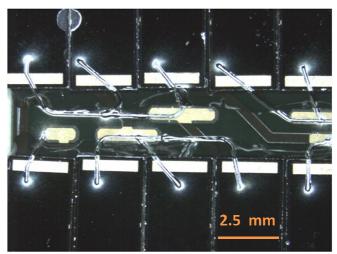

Figure 11: Image of the interconnect details between the substrate and the die, the interconnection realized using conventional packaging methods (wire bonding and encapsulation).

Figure 12: Image of the interconnect details between the substrate and the die, the interconnection realized by AJP silver layer.

### **Electrical characterization**

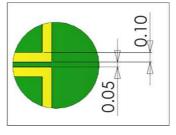

We performed extensive electrical characterization of the AJP deposited silver track line ( $60\mu m$  width,  $3\mu m$  thickness and 20mm length). For each lot of samples for the electrical measurements we selected randomly 3 samples.

Figure 13: Layout of the test substrate for the electrical evaluation. All dimensions are in mm.

Figure 14: Details of the conductive track on the test substrate. All dimensions are in mm.

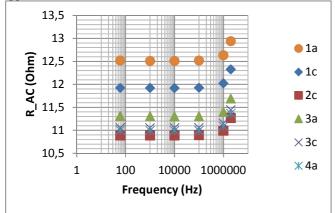

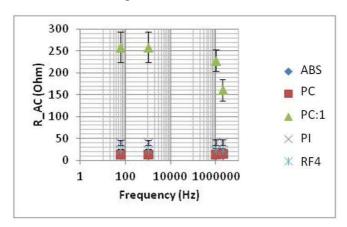

We used 4 point measurement method and performed the electrical measurements on DC, and AC at six following frequencies: 60Hz, 1kHz, 10kHz, 100kHz, 1MHz and 2MHz. Till the frequency of 100kHz the value of resistivity remains practically constant.

We compared the result of the electrical measurements with the manufacture (Cabot) datasheet. The lowest resistance value provided by Cabot for the CSD-32 nano-silver ink is in the range of 3-4  $\mu$ Oh\*cm and can be achieved by sintering the samples at 250°C for 30min [7]. According to the Cabot 30  $\mu$ Oh\*cm is the best value for 150°C for 30min.

The experimentally obtained value of the resistivity on our test samples is 16  $\mu$ Oh\*cm, that is in 10 higher than the resistivity of bulk silver of 1.6  $\mu$ Oh\*cm, however it is in line with resistivity of thin film silver tracks applied by other deposition methods and low enough to support many

applications.

Figure 15: The resistance of AJP silver conductive track on ABS substrate of 6 samples.

Figure 16: The resistance of AJP silver conductive track on ABS, PC, PC:1 (single layer), PI and FR4 substrates.

The figure 15 and 16 depict plots of electrical resistance versus frequency of the silver tracks processed on the organic substrates. On all substrates in study, except one: PC:1 (single layer of silver ink deposited on polycarbonate substrate, figure 16) we deposited sequentially 2 layers of AJP silver ink. We experimentally learnt that single-layer of silver ink deposition is not sufficient to form an even and continuous of silver ink track; remarkably that the substrates in study have different roughness and porosity that has direct effect on the silver track properties. The single layer silver track for the sample PC:1 has the electrical resistivity from 5 to 10 time higher than 2 layers track.

### **Conclusions**

Apparently the wire bonding on AJP deposited silver layer has limited bondability in terms of Au and Al wire bonding and a status as on the date of preparing the paper the AJP deposited silver layer can't be used for mass scale production. We consider that fact not as a drawback for the AJP technology, the AJP silver track as an alternative to the

conventional interconnect technology, specifically for the wire bonding. AJP deposited silver layer on all evaluated substrates (PI, FR4, PC and ABS) are suitable for surfacemount technology using the conductive adhesive, and additionally to that AJP on PI and FR4 are suitable for soldering technique. The value of the resistivity is 16 μOh\*cm, that is higher than the resistivity of bulk silver of 1.6 μOh\*cm, however the value is in line with resistivity provided by the manufacture's datasheet, and similar as for thin film silver conductive tracks applied by other deposition methods. The resistivity is low enough to support many applications. We also demonstrated that for specific application (Autonomous Wireless Sensor Node prototype) the conventional interconnection technique as the wire bonding can be successfully replaced by AJP deposited conductive silver track.

#### Acknowledgments

The authors would like to acknowledge support from Microsys/ULG, Sirris and DICE/UCL. The research has been carried out in the frame of the Minatis project. The project is performed with the support of the Walloon Region of Belgium, European Union (FEDEX fund) and is carried out by a consortium of research institutions.

#### References

- Martin Hedges, Mike Kardos, Bruce King, Mike Renn. Aerosol-Jet Printing for 3-D Interconnects, Flexible Substrates and Embedded Passives. Proceedings of the International Wafer Level Packaging Conference, San Jose, CA, November, 2006.

- 2. Matthias Hörteis, Stefan W. Glunz. Fine Line Printed Silicon Solar Cells Exceeding 20% Efficiency: *Progress in Photovoltaics: Research and Applications* 2008; 16:555–560.

- 3. Bruce King, Mike Renn. Aerosol Jet® direct write printing for mil-aero electronic applications, published on www.optomec.com

- 4. Martin Hedges, Aaron Borras Marin 3D Aerosol Jet® Printing Adding Electronics Functionality to RP/RM Presented at DDMC 2012 Conference, March 14-15, 2012, Germany, Berlin.

- 5. W. Verheecke etc, Optimization Aerosol Jet Printing of silver interconnects on polyimide film for embedded electronics applications, 8<sup>th</sup> International DAAAM Baltic Conference "Inductrial Engineering", 19\_21 April 2012, Tallinn, Estonia, in Conf. Proc. pp.373-379.

- 6. "Nanotechnologies and Electronics Packaging" by James E. Morris, 2008

- 7. Datasheet CSD-32, Cabot printed Electronics Materials.

- 8. D.Vandormael et al., "Direct deposition of surface acoustic wave sensors by aerosol jet printing technique", in Proc. Smart Systems Integration (SSI) Conf., Zurich, Switzerland, March 21-22, 2011.paper 32

- 9. G.Harman "Wire Bonding in Microelectronics: Materials, Processes, Reliability, and Yield", McGraw-Hill Professional; 3d edition, 2010. 290p.

- 10. www.engineeringtoolbox.com (material properties).